Electronic Technology Forum

Overview MOS integrated circuit design basic circuit examples and detailed explanations

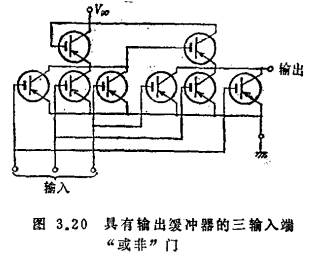

Figure 3.20 is a NOR gate circuit composed of P-channel transistors. This circuit adopts the form of leaking ground and is equipped with output buffer. Circuits in large-scale integrated circuits are also commonly combined with such gate circuits.

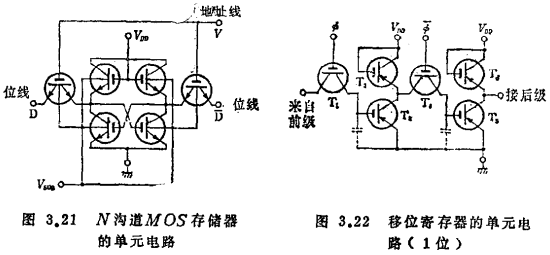

The N-channel 144-bit memory is developed as a high-speed MOS memory 18), and the unit circuit used in this memory is shown in Figure 3.21. It is a simple circuit composed of a flip-flop and a write-read gate. In order to achieve a high-speed write time of 40 nanoseconds, we use an N-channel with high mobility. Since the MOS tube made by the usual process is depletion type, current flows when the gate bias is zero, but after the substrate is reverse biased, it becomes an enhanced type with a positive threshold voltage, and the components are isolated from each other of.

Figure 3.22 shows a part of the shift register circuit. T1 and T4 are used as transmission gates, just add clocks to each time,The state of the previous stage is transferred. The clock signals added to the T1 address line and T4 are inverse to each other, and the clock signal is actually generated by a single-phase pulse through two inverters. The gate capacitance of T2 and T5 is used for temporary storage. The maximum integration level is 200-bit monolithic integration, and there are also reports of large-scale integrated circuits integrating 2,000 bits on the substrate 19).

time,The state of the previous stage is transferred. The clock signals added to the T1 address line and T4 are inverse to each other, and the clock signal is actually generated by a single-phase pulse through two inverters. The gate capacitance of T2 and T5 is used for temporary storage. The maximum integration level is 200-bit monolithic integration, and there are also reports of large-scale integrated circuits integrating 2,000 bits on the substrate 19).

Contact: Mr. Zou

Contact number: 0755-83888366-8022

Mobile phone: 18123972950

QQ: 2880195519

Contact Address: 5C1, Block CD, Tianji Building, Tianan Digital City, Chegongmiao, Futian District, Shenzhen

Please search WeChat official account: "KIA Semiconductor" or scan the following picture to "Follow" official WeChat official account

Please "follow" the official WeChat account: provide MOS tube technical assistance