Electronic Technology Forum

Detailed explanation of MOS integrated large-scale integrated circuit design and measures

This section studies the design of large-scale integrated circuits from the perspective of system design. What kind of problems will arise after increasing the integration level? What measures are taken to address these issues? We use specific examples of large-scale integrated circuit products to illustrate the above problems.

The general trend is that the higher the degree of integration of integrated circuits, the less freedom of integrated circuit functions. On the other hand, because large-scale integrated circuits require a large amount of research and development funds, it is necessary to produce as many circuits as possible to improve the economic effect of mass production. Solving the contradiction between the two is a major issue for large-scale integrated circuits. MOS integrated large-scale integrated circuit design. In the early stage of the commercialization of large-scale integrated circuits, this problem was mainly manifested in system division, that is, when a system is composed of several large-scale integrated circuits, how to divide the system to increase the degree of freedom of each large-scale integrated circuit function .

(1) System partition

When a system is integrated into a large-scale integrated circuit, there is no problem of system partitioning. However, considering the integration degree of large-scale integrated circuits that was technically possible at that time, when the entire system must be composed of more than two large-scale integrated circuits, then System partition must be performed. Generally, the following points should be considered when performing system partitioning.

(I) Maximize the degree of freedom in the functions of each large-scale integrated circuit.

(Ii) The signal exchange between the divided subsystems should be as little as possible.

(Iii) All kinds of large-scale integrated circuits are divided with equal integration.

The consideration method focusing on the above item (i) is developed from the consideration method of medium-scale integrated circuits. The entire system is divided into functionally complete subsystems and each subsystem is standardized, thereby increasing each large-scale Degree of freedom in the function of integrated circuits. This method is difficult to achieve the equalization of the integration level of item (iii) above. MOS integrated large-scale integrated circuit design. In addition, complicated parts such as control circuits are difficult to separate due to the limitation of the number of leads of large-scale integrated circuits. At the same time, standardization is also difficult. Therefore, there are various difficulties in dividing the system by focusing on item (i). On the other hand, when a large number of large-scale integrated circuit products are required, item (iii) is more important than item (i), depending on the degree of integration possible at the time and the limitation of the number of leads. Make the most appropriate segmentation. This is the system partitioning method used in the early stage of large-scale integration.

However, the above-mentioned "best" segmentation method will make the degree of freedom in the function of the large-scale integrated circuit become very small, and it is difficult to adapt to the changes in the market demand in terms of specifications and varieties. Therefore, it is impossible to realize the large-scale integrated circuit in a small-volume model化. In order to solve such requirements for large-scale integrated circuits, the following measures can be taken.

(2) Program logic array structure

For desktop computers, the entire system can be roughly divided into the following two parts:

(I) The program generating circuit that specifies the calculation program;

(Ii) The arithmetic part of the circuit instruction generated by the execution program.

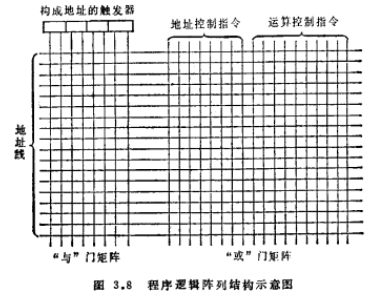

Among the above parts, most of the parts that change with the specifications of the system are (i) the program generating circuit part, and the (ii) calculation part is easier to standardize. The program logic array structure mentioned here is mainly a large-scale integrated circuit design method considered for the standardization of part (i). As shown in Figure 3.8, it is composed of an AND gate matrix and an OR gate matrix. Arranging this part previously composed of random logic into a neat matrix form makes it easy to change this part, so that systems of various specifications can be made by changing the mask pattern of the large-scale integrated circuit. MOS integrated large-scale integrated circuit design. If only the original program generating circuit is arranged in a matrix form, its efficiency is extremely low, and the number of leads is too large, which is very impractical, and measures must be taken to improve it. In order to solve this problem, microinstructions were output directly from each address line in the past, but when the program logic array structure is adopted, the coded microinstructions are output from the address lines. The step of converting into microinstructions is to accept large-scale integration of instructions. On the side of the circuit. As a result, not only the number of signal exchanges between large-scale integrated circuits can be reduced, but the efficiency of the OR gate array is also improved.

The above describes the means to improve the degree of freedom from the aspect of the degree of freedom in the function of the large-scale integrated circuit. In addition, issues that should be considered from the perspective of system design include power consumption and inspection methods.

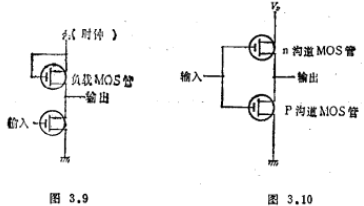

Reducing the power consumption of the basic circuit of a large-scale integrated circuit is directly related to improving the integration level, and a circuit structure with low power consumption should be selected as far as possible. In addition, power consumption is also closely related to operating speed. Generally, there is a tendency to increase power consumption and reduce integration to increase speed. Therefore, when designing large-scale integrated circuits, we must fully consider the operating speed required by the system in order to reduce costs and improve performance. In order to reduce power consumption, various measures have been tried, examples of which are shown in Figure 3.9 and Figure 3.10. The circuit in Figure 3.9 only supplies power when it is necessary for signal transfer, so there is no unnecessary power consumption. Figure 3.10 is an example of a complementary circuit. Compared with the original circuit with load resistance, it has no DC current, so the power supply efficiency is greatly improved.

Finally, there is the question of detection. It is technically difficult to detect unqualified integrated circuits with 100% accuracy. But in fact, according to the management requirements of the production process, a 100% failure detection rate is not necessarily required. There is a certain relationship between the detection time and the failure detection rate. According to the convenience of process management, appropriate methods can be considered. In the production process of large-scale integrated circuits, the testing process accounts for a large proportion. When designing large-scale integrated circuits, logic design and circuit design that can save testing time should be considered.

When researching and trial-manufacturing large-scale integrated circuits, it is necessary to test whether the circuit fully meets the predetermined function, but this is very different in nature from the above-mentioned test from the perspective of process management. MOS integrated large-scale integrated circuit design. In the former case, the test pattern is generally made and the computer is used for automatic detection. In the latter case, the trial-produced large-scale integrated circuit is installed in the simulation device, and the work of the entire system is checked by humans. This is the most effective method at present.

Contact: Mr. Zou

Contact number: 0755-83888366-8022

Mobile phone: 18123972950

QQ: 2880195519

Contact Address: 5C1, Block CD, Tianji Building, Tianan Digital City, Chegongmiao, Futian District, Shenzhen

Please search WeChat official account: "KIA Semiconductor" or scan the following picture to "Follow" official WeChat official account

Please "follow" the official WeChat account: provide MOS tube technical assistance