Electronic Technology Forum

Detailed explanation of the circuit diagram of a sinusoidal oscillator composed of a switched capacitor circuit

1. Switched capacitor sine oscillator

The sine oscillator composed of a double second-order switched capacitor circuit (Figure 5.3-12c) is shown in Figure 6.2-3. The op amps A1, A2 and capacitors CA, CB, CC, CD, CE, and CH in the picture form a stable high-Q double second-order switched capacitor circuit. If the node N1 is a square wave signal, due to the filtering effect of the biquad circuit, a sinusoidal signal is obtained at the output end of A1 or A2. Op amp It forms a positive feedback path with the switched capacitor image.png to make the circuit oscillate. In order to explain its oscillation principle, the output terminal of the operational amplifier A3 and node N1 are newly opened. At this time, if a signal source voltage is added to the node N1, this voltage is in the same phase as the voltage at the output terminal V1 of the op amp A1, and the V1 voltage is then amplified in phase by the op amp A2 (comparator), and the output terminal is the limiter. Wave voltage, this voltage is much greater than the input signal source voltage on the N1 node, so the loop gain of the positive feedback is greater than 1. Therefore, after the node N1 is connected to the output terminal of A3, oscillation must occur, and the voltage on the node N1 is a square wave voltage, and its positive and negative levels are the limiting levels of the output of A3. Let A3 output limiter level be

It forms a positive feedback path with the switched capacitor image.png to make the circuit oscillate. In order to explain its oscillation principle, the output terminal of the operational amplifier A3 and node N1 are newly opened. At this time, if a signal source voltage is added to the node N1, this voltage is in the same phase as the voltage at the output terminal V1 of the op amp A1, and the V1 voltage is then amplified in phase by the op amp A2 (comparator), and the output terminal is the limiter. Wave voltage, this voltage is much greater than the input signal source voltage on the N1 node, so the loop gain of the positive feedback is greater than 1. Therefore, after the node N1 is connected to the output terminal of A3, oscillation must occur, and the voltage on the node N1 is a square wave voltage, and its positive and negative levels are the limiting levels of the output of A3. Let A3 output limiter level be , Then the voltage on node N1 is the amplitude of soil

, Then the voltage on node N1 is the amplitude of soil / Of the square wave voltage. Switched capacitor sinusoidal oscillator. Let's derive the expressions of the output voltages V1 and V2. In order to facilitate analysis, disconnect the output terminal of A3 from node N1, and connect the switch capacitor in the graph of the square wave voltage Vin with an amplitude of 1 to node N1

/ Of the square wave voltage. Switched capacitor sinusoidal oscillator. Let's derive the expressions of the output voltages V1 and V2. In order to facilitate analysis, disconnect the output terminal of A3 from node N1, and connect the switch capacitor in the graph of the square wave voltage Vin with an amplitude of 1 to node N1 equivalent resistance

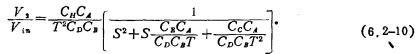

equivalent resistance and T/Cc. In this way, the following relationship can be obtained from Figure 6.2-3:

and T/Cc. In this way, the following relationship can be obtained from Figure 6.2-3:

The transfer function of the second-order band pass filter is obtained from the above formula

And the standard form of the second-order bandpass transfer function is

Let equation (6.2-6) be equal to equation (6.2-7), and obtain the gain Ao at the center angular frequency ωo, Q, and ωo:

From Fourier analysis, it can be seen that the voltage amplitude is a square wave of image.png, and the amplitude of its fundamental wave is image.png. Therefore, at ωo, the output voltage V1 of the op amp A1 can be written as Square wave, the amplitude of the fundamental wave is

Square wave, the amplitude of the fundamental wave is . Therefore, at ωo, the output voltage V1 of the op amp A1 can be written as

. Therefore, at ωo, the output voltage V1 of the op amp A1 can be written as

It can be obtained from the formula (6.2-5) the transfer function is

the transfer function is

The above equation is the transfer function of the second-order low-pass filter, and its pole frequency ωo and Q value expression are the same as equation (6.2-8). At ωo, the output voltage V2 of the op amp A2 is expressed as

Op amp  after the output terminal is connected to the node N1, as a positive feedback loop is formed, the amplitude value obtained at the node N1 is soil

after the output terminal is connected to the node N1, as a positive feedback loop is formed, the amplitude value obtained at the node N1 is soil  after the voltage is filtered by high-Q band-pass and low-pass, a sinusoidal signal with a frequency of ωo is obtained at the output of A1 and A2. The amplitude is determined by (6.2-9) and (6.2- 11) Formula expression. The following discusses the harmonic components of the V1 and V2 voltages.

after the voltage is filtered by high-Q band-pass and low-pass, a sinusoidal signal with a frequency of ωo is obtained at the output of A1 and A2. The amplitude is determined by (6.2-9) and (6.2- 11) Formula expression. The following discusses the harmonic components of the V1 and V2 voltages.

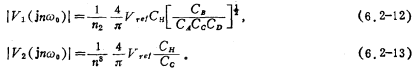

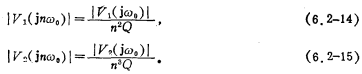

It can be obtained from equations (6.2-6) and (6.2-10), the expressions of V1 and V2 when the harmonic frequency is nωo:

(6.2-12) and (6.2-9), (6.2-13) and (6.2-11), the relationship between the n-th harmonic output voltage and the fundamental output voltage is

From equations (6.2-14) and (6.2-15), it can be seen that the harmonic component of the output voltage of V2 is 1/n times the harmonic component of the output voltage of V1, so the output terminal of the sinusoidal signal is V2. For the third harmonic component, under the condition of Q=10, the harmonic component of the output voltage of V1 is -39 decibels, and the harmonic component of the output voltage of V2 is -48.6 decibels.

2. Improved form of switched capacitor sinusoidal oscillator

The working principle of the circuit in Figure 6.2-3 is discussed above, and the output amplitude, frequency and harmonic components of the sinusoidal signal are analyzed. (6.2-8~11) formula provides the design formula of this circuit. From the formulas (6.2-9) and (6.2-11), the output amplitude of the sine signal depends on the output limiting level of the operational amplifier A3 . In order to obtain a stable output amplitude,

. In order to obtain a stable output amplitude,  Can be replaced by reference voltage. In addition, the circuit in Figure 6.2-3 often stops vibration due to operational amplifier voltage imbalance and other reasons. In order to overcome this shortcoming, a non-limiting positive feedback loop to ensure vibration is introduced. After the above improvements, the circuit form is shown in Figure 6.2-4. When the circuit just starts to work, the FET M1 is cut off, and C3 and C3 are connected in series to form a positive feedback path to ensure that the circuit starts to oscillate. If it starts to oscillate, the op amp A3 limits the output voltage V1 of A1 to make it a square wave. This voltage passes through an inverter to get image.png and the signal respectively. image.png and image.png The enhanced NMOS transistors M2, M3, M4, and M5 connected to the diode form a full-wave rectifier circuit, which feeds positive charge into the parasitic capacitance of the gate of M1 to ground, turns on M1 and cuts off the image. The positive feedback path of png. By the function of image.png, another positive feedback path is formed through DC reference voltage image.png, capacitor CH and input circuit switch. During the oscillation of the circuit, image.png is in phase with V1 and inverted with V1. For V1>0,

Can be replaced by reference voltage. In addition, the circuit in Figure 6.2-3 often stops vibration due to operational amplifier voltage imbalance and other reasons. In order to overcome this shortcoming, a non-limiting positive feedback loop to ensure vibration is introduced. After the above improvements, the circuit form is shown in Figure 6.2-4. When the circuit just starts to work, the FET M1 is cut off, and C3 and C3 are connected in series to form a positive feedback path to ensure that the circuit starts to oscillate. If it starts to oscillate, the op amp A3 limits the output voltage V1 of A1 to make it a square wave. This voltage passes through an inverter to get image.png and the signal respectively. image.png and image.png The enhanced NMOS transistors M2, M3, M4, and M5 connected to the diode form a full-wave rectifier circuit, which feeds positive charge into the parasitic capacitance of the gate of M1 to ground, turns on M1 and cuts off the image. The positive feedback path of png. By the function of image.png, another positive feedback path is formed through DC reference voltage image.png, capacitor CH and input circuit switch. During the oscillation of the circuit, image.png is in phase with V1 and inverted with V1. For V1>0, (高电乎),电容CH 显反相连接方式,若

(高电乎),电容CH 显反相连接方式,若 ,CH在每个时钟周期间隔向电容

,CH在每个时钟周期间隔向电容 feed negative charge

feed negative charge . Make V1 rise further. Similarly, for V1<0,

. Make V1 rise further. Similarly, for V1<0, , CH is connected in phase, and CH will be

, CH is connected in phase, and CH will be feed positive charge

feed positive charge , Make V1 fall further. Obviously, it is a positive feedback loop. In addition,

, Make V1 fall further. Obviously, it is a positive feedback loop. In addition, It is a negative feedback loop to limit the amplitude of oscillation. Sample-and-hold circuits M6 and C1 provide a clock cycle delay for the positive feedback loop to prevent parasitic oscillation. due to

It is a negative feedback loop to limit the amplitude of oscillation. Sample-and-hold circuits M6 and C1 provide a clock cycle delay for the positive feedback loop to prevent parasitic oscillation. due to

Using the reference voltage, the output signal amplitude of the circuit in Figure 6.2-4 will be very stable. The above analysis shows that it is no different from the working principle of the circuit in Figure 6.2-3. The various relational expressions ((6.2-6)~(6.2-15) equations) for the circuit in Figure 6.23-3 are also applicable to the circuit in Figure 6.2-4.

If image.png contains a modulated signal, then the oscillation circuit in Figure 6.2-4 can also generate an amplitude modulated sine wave. If you change the value, you can control the oscillation frequency to achieve frequency shift keying (FSK) and programmable frequency oscillation.

value, you can control the oscillation frequency to achieve frequency shift keying (FSK) and programmable frequency oscillation.

Contact: Mr. Zou

Contact number: 0755-83888366-8022

Mobile phone: 18123972950

QQ: 2880195519

Contact Address: 5C1, Block CD, Tianji Building, Tianan Digital City, Chegongmiao, Futian District, Shenzhen

Please search WeChat official account: "KIA Semiconductor" or scan the following picture to "Follow" official WeChat official account

Please "follow" the official WeChat account: provide MOS tube technical assistance