Electronic Technology Forum

Equiplanar silicon gate N-channel MOS process manufacturing steps and characteristics

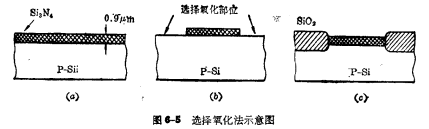

N-channel and other planar technology, also known as "selective oxidation MOS technology", its characteristic is to selectively oxidize a certain part of the silicon substrate, but not The area that needs to be oxidized is protected with a  mask. Its basic method is shown in Figure 6-5. First, a thin layer of

mask. Its basic method is shown in Figure 6-5. First, a thin layer of  is deposited on the silicon substrate, The thickness is about 0.2~0.9μm, then, engrave the part that needs to be oxidized

is deposited on the silicon substrate, The thickness is about 0.2~0.9μm, then, engrave the part that needs to be oxidized  The film is then oxidized by thermal oxidation to form a layer of about 1.0μm~1.1μm oxide layer. Since

The film is then oxidized by thermal oxidation to form a layer of about 1.0μm~1.1μm oxide layer. Since  The thermal oxidation rate of the film is extremely slow, and it has a negative effect on the oxygen atmosphere. Masking effect, so

The thermal oxidation rate of the film is extremely slow, and it has a negative effect on the oxygen atmosphere. Masking effect, so  The part under the film is not oxidized. In the oxidized area, as the thickness of the oxide layer increases, the silicon-silicon dioxide interface gradually moves toward the depth of the substrate, so there is approximately Half of the

The part under the film is not oxidized. In the oxidized area, as the thickness of the oxide layer increases, the silicon-silicon dioxide interface gradually moves toward the depth of the substrate, so there is approximately Half of the  , the film is on the surface, and the other half is accompanied by Below the surface. In this way, most of the thick

, the film is on the surface, and the other half is accompanied by Below the surface. In this way, most of the thick  layer is buried in the surface of Si , Make the surface relatively flat. The device is made on the junction surface higher than the oxide layer.

layer is buried in the surface of Si , Make the surface relatively flat. The device is made on the junction surface higher than the oxide layer.

In the discussion of the conventional MOS process, it is known that in order to obtain a higher field threshold voltage, the primary oxidation often needs to be made very thick. Finally, when the lead hole is carved, it will cause a lot of The high silicon dioxide step, so the metal interconnection line must exceed the steep pin step formed by the oxide. Silicon gate N-channel MOS process. At these steps, the metal layer is thin, and it is easy to cause disconnection and open circuit. Even if there is no fracture at the beginning, the current density is high in the thin metal area, which causes electromigration, and the disconnection occurs in some places, which makes the device early Invalidate. By adopting the above-mentioned isoplanar process, since the silicon dioxide layer is buried in the substrate, the steep silicon dioxide step in the conventional process is eliminated, and the reliability of the device is greatly improved.

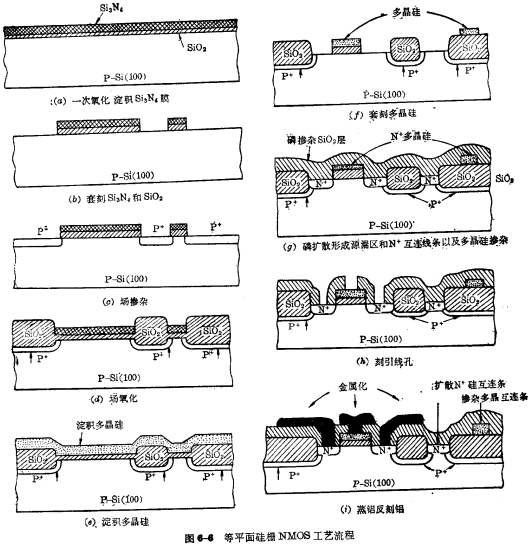

1. Manufacturing steps of silicon gate N-channel MOS process

(1) Primary oxidation and deposition film

film

Take a P-type silicon single wafer with a resistivity of 3~5Ωcm (100) crystal plane, after chemical cleaning, perform an oxidation (to be the insulating gate of the device), and the thickness is 100~120nm; Then, use silicon tetroxide to decompose in ammonia gas, and deposit a layer on the silicon wafer Film, the temperature is about 850℃.

Film, the temperature is about 850℃.

(2) Overlay engraving of silicon nitride and silicon dioxide

After overprinting, only the silicon dioxide and silicon nitride layers are left in the parts where the source, drain, channel regions and diffusion interconnections are to be formed later, and the other parts Have been carved away.

(3) Field doping

First, under the condition of 460℃, a layer of boron-doped silicon dioxide is deposited on the surface of the silicon wafer by thermal decomposition; The silicon surface diffuses, so that the unmasked part (called the field) is doped with a certain amount of boron.

(4) Field oxidation (thick oxide layer formation)

First, the doped oxide is etched away, and then under the humid oxygen condition of 975℃, Partially oxidize the unmasked boron-doped area to grow a thick oxide layer of about 1000~1100nm. Silicon gate N-channel MOS process. About half is below the original surface of the silicon, and the other half is above the surface.

(5) Depositing polysilicon

First, the silicon nitride film is etched away, and the remaining silicon dioxide film is used as the insulating gate dielectric of the device. After annealing the wafer in high-temperature nitrogen, a layer of polysilicon film is deposited on the surface of the wafer, approximately 480~500nm. Finally, perform thermal oxidation treatment.

(6) Overlay engraved polysilicon

Engrave the diffusion window of the source and drain regions and the diffusion bar of the external connection.

(7) Phosphorus diffusion

A layer of heavy phosphorus-doped silicon dioxide is thermally decomposed and deposited on the surface of the silicon wafer, and then the silicon wafer is pushed into a constant temperature zone of about 1050℃, Medium treatment for 10-15 minutes. In this way, phosphorous diffusion is carried out to form the source and drain with a diffusion depth of about 1Ωm and the N+ region of the doped interconnection line. At the same time, the polysilicon is also doped.

(8) Lithography leadhole

Provide metal contacts between source, drain and gate.

(9) Steamed aluminum, reverse engraving

In some processes, a thin layer of titanium is vaporized before aluminum is vaporized, and then aluminum is vaporized to form a titanium-aluminum double-layer metal. This is particularly advantageous for N-channel MOS integrated circuits, because the titanium layer can prevent the aluminum layer from failing due to the dislocation and shrinkage of the shallow N+ diffused junction.

After reverse engraving, alloy treatment is carried out in hydrogen at 480℃ for 30 minutes to ensure good contact between metal and silicon and eliminate the surface state of the silicon-silicon dioxide interface. Silicon gate N-channel MOS process. Finally, a low-temperature deposition method is used to grow a 500nm-thick silicon dioxide protective film on the surface of the wafer.

The specific process is shown in Figure 6-6(a)~(c).

2. Discussion on process characteristics of silicon gate N-channel MOS process

Using isoplanar technology to manufacture N-channel MOS circuits, in addition to the relatively flat surface introduced above, there is no steep oxide layer step, and the metal leads are not prone to breakage. From the perspective of the entire production process, there are other more prominent advantages.

(1) Partially dope the silicon surface in the thick oxide area (field area). Through local doping, the surface concentration of these areas is increased to make the field threshold voltage greatly improved. When the junction of the source, drain, and channel regions of the tube is made, the original village bottom concentration is still maintained, so the channel mobility of the tube will not be reduced, and the circuit speed will be improved from the surface.

greatly improved. When the junction of the source, drain, and channel regions of the tube is made, the original village bottom concentration is still maintained, so the channel mobility of the tube will not be reduced, and the circuit speed will be improved from the surface.

(2) From Figure 6-7 that due to the field doping, the field diffusion region can act as an isolation, so that the parasitic trench between the N+ regions of adjacent devices Channel leakage is reduced to a minimum. Silicon gate N-channel MOS process. Therefore, the distance between the devices can be shortened, thereby greatly improving the integration level of the circuit.

that due to the field doping, the field diffusion region can act as an isolation, so that the parasitic trench between the N+ regions of adjacent devices Channel leakage is reduced to a minimum. Silicon gate N-channel MOS process. Therefore, the distance between the devices can be shortened, thereby greatly improving the integration level of the circuit.

(3) Because the substrate concentration in the mesa area where the device is made is low, it is estimated that the threshold voltage of the tube is VT< /span>About 0.2V~0.6V, is obviously a bit lower. In order to increase the value of the threshold voltage, the backside gate effect can be used to apply a negative bias to the substrate to make VT is adjusted to 1.4V~2.0V. After adding a negative substrate bias, the field threshold voltage of the thick oxide region can be increased to 10V~20V, which meets the requirements of circuit operation.

(4) A diode formed between the diffused N+ region and the field-doped P+ region, Can be used as a gate protection device.

Because of the high acceptor concentration on the surface of the field-doped P area, the avalanche breakdown voltage of this diode is between 20V and 30V, and it is hard breakdown. Silicon gate N-channel MOS process. Therefore, this kind of gate protection device does not need to cover a grounded gate electrode around the diffusion junction like the gate protection device of a common MOS circuit.

(5) In the above process, the silicon gate process is also used, so it also has all the advantages of the silicon gate process.

Although the above-mentioned process is more complicated than the conventional MOS process, with the development of science and technology, the planar silicon gate NMOS process has become an important means of manufacturing large-scale MOS integrated circuits.

Contact: Mr. Zou

Tel: 0755-83888366-8022

Mobile: 18123972950

QQ: 2880195519

Address: 5C1, CD Block, Tianji Building, Tian’an Digital City, Chegongmiao, Futian District, Shenzhen

Please search the WeChat official account: "KIA Semiconductor" or scan the picture below to "Follow" the official WeChat official account

Please "Follow" the official WeChat account: provide MOS tube technical assistance