Electronic Technology Forum

Detailed description of main parameters and important parameters of MOS tube

1. MOS tube DC parameters

1. Drain-source cut-off current Ioff

For an enhanced MOS tube, when VGS=0, the tube is cut off and the drain and source cannot be conducted, that is, the drain-source current should be zero. However, due to the reverse leakage of the PN junction, there is still a small leakage current between the drain and the source, which is often referred to as the cut-off leakage current, which is represented by Ioff. In fact, the leakage caused by not only the reverse leakage of the PN junction, but also the leakage of the channel.

2、Saturated drain current IDSS

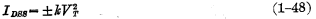

For a depletion-type MOS tube, when VGS=0, the channel already exists, and the drain and source diffusion regions of the MOS tube are already conducting. When VGS is constant and large enough, the saturation value of the drain current is called the saturation drain current of the MOS tube, which is represented by IDSS. The main parameters of MOS tube. According to the saturation current formula of the MOS tube, substituting VGS=0, the saturation drain current of the depletion-type MOS tube can be obtained as:

This value is positive for N-channel depletion MOS transistors, and negative for P-channel depletion MOS transistors.

3、Gate source DC input impedance

The gate and source of the MOS tube are separated by a gate dielectric SiO2 insulating layer. When forming a circuit, the gate and source are usually used as input terminals.The so-called gate source DC input impedance  is the insulation resistance of the SiO2 layer. The main parameters of MOS tube. The thicker the gate oxide layer, the better the quality, and the higher the insulation resistance. If the thermally grown SiO2 has a complete structure and the thickness is about 150nm, the insulation resistance can reach 1012Ωabove,If a certain voltage is applied between the gate and the channel, the current that can pass through the gate oxide is extremely small, generally less than 10-14A. This is one of the valuable characteristics of the MOS tube.

is the insulation resistance of the SiO2 layer. The main parameters of MOS tube. The thicker the gate oxide layer, the better the quality, and the higher the insulation resistance. If the thermally grown SiO2 has a complete structure and the thickness is about 150nm, the insulation resistance can reach 1012Ωabove,If a certain voltage is applied between the gate and the channel, the current that can pass through the gate oxide is extremely small, generally less than 10-14A. This is one of the valuable characteristics of the MOS tube.

4、On resistance

When the MOS tube is working in the unsaturated zone, the VDS is very small, and the characteristic curve is a straight line, that is, IDS is proportional to VDS. At this time, the tube is equivalent to a pure resistance, that is, when the VDS is very small, the formula (1-46) can be omitted In this term, the current formula in the unsaturated zone can be written as:

In this term, the current formula in the unsaturated zone can be written as:

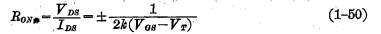

In this case, the ratio of the drain-source voltage to the drain-source current IDS is called on-resistance, which is often expressed as RON.

It can be seen that the on-resistance is inversely proportional to (VGS-VT). When VGS≈VT, RoN becomes very large, that is, the inversion layer almost disappears . In addition, RoN is proportional to the channel length L, and is proportional to the channel width W is inversely proportional.

It is conceivable that if VDS-VGS-VT, the work of the MOS tube goes into saturation, the channel resistance at this time should be:

It can be seen that the channel on-resistance at critical saturation is twice the on-resistance of the unsaturated zone.

5、Drain-source breakdown voltage BVDS

In the previous discussion of the output characteristic curve of the MOS tube, it was mentioned that when the drain-source voltage VDS exceeds a certain limit, breakdown will occur and the leakage current will increase sharply. The drain-source breakdown voltage is determined by two factors:

(1)PN junction breakdown between the drain diffusion region and the substrate

When the source of the MOS tube is connected to the substrate, applying a voltage between the drain and the source is equivalent to applying a reverse voltage on the PN junction between the drain and the substrate. When the VDS is very large, the depletion zone of the PN junction becomes very wide, and the electric field in the barrier zone becomes very large. When the VDS reaches a certain value, lightning avalanche breakdown occurs in the barrier zone and the depletion layer This is exactly the same as the PN junction breakdown of a bipolar tube. The main parameters of MOS tube. However, it must be pointed out that for MOS devices, since the source and drain diffusion regions are generally shallow junction diffusion, the electric field distribution diagram of the depletion region near the drain diffusion region in Fig. 1-26 has a large bend at the edge of the shallow PN junction. There will be a strong corner electric field, so the PN junction breakdown occurs here first, causing the BVDS to be greatly reduced. In addition, for the diffusion area of the MOS tube, the metal gate electrode covers the edge of the diffusion area, as shown in Figure 1-28. Due to the influence of the gate electric field, the size of the breakdown voltage will also be greatly affected. For example, assuming that VDS=20V and VGS=5V, the gate electrode is at a negative potential relative to the drain electrode. Therefore, the electric field of the covered part of the gate electrode and the drain electrode will be strengthened and the breakdown voltage will be reduced.

(2)Punch-through phenomenon between drain and source

For an enhanced device, in general, when Vs=0 and VGs=0, there is no channel on the silicon surface, and there is no conduction between the source and the drain. When a voltage is applied between the drain and the source, there will only be a very small reverse leakage current of the PN junction. However, as the VDS continues to increase, the depletion layer near the drain region also expands accordingly. When the VDS is large to a certain extent and the depletion layer around the drain region extends to overlap with the source diffusion region, a large number of electrons in the source diffusion region will pass through the depletion region directly from the source diffusion region under the action of a strong electric field. The area is swept into the drain area, and a large current is generated, which is the drain-source punch-through effect. As shown in Figure 1-29.

Especially for MOS transistors with a relatively high substrate resistivity p and a relatively small channel length L, it is easier to form a punch-through phenomenon.

The punch-through voltage is the same as the breakdown voltage, which limits the maximum drain-source operating voltage VDS. For a specific tube, whether the PN junction breakdown occurs first or the punch-through phenomenon occurs first depends on the specific structure. If the substrate resistivity is low and the channel is longer, the BVDS is always determined by the avalanche breakdown voltage. The main parameters of MOS tube. For a tube with a higher substrate resistivity and a shorter channel length L, a punch-through phenomenon can occur before the avalanche breakdown occurs.

For shallow junction diffusion on a high-resistivity substrate material, the width of the depletion layer can be approximated by a sudden junction, and the thickness of the depletion layer is:

Among them, V here is VDS, and VD is the self-built potential of PN junction. When image.png, the punch-through effect occurs. If VD is omitted, the drain-source breakdown voltage caused by the punch-through phenomenon is:

For the doping concentration of 5×1014/cm2 (equivalent to p-10 .cm) P-type substrate, made into channel length

.cm) P-type substrate, made into channel length MOS tube, calculated according to formula (1-53),

MOS tube, calculated according to formula (1-53),  about It is 35~40V, which is much lower than the general PN junction breakdown voltage. Therefore, the actual measured drain-source breakdown voltage is caused by the punch-through phenomenon.

about It is 35~40V, which is much lower than the general PN junction breakdown voltage. Therefore, the actual measured drain-source breakdown voltage is caused by the punch-through phenomenon.

6、Gate breakdown and gate protection

(1)Gate breakdown

In a MOS tube, there is an oxide film between the gate and the channel. This structure is the same as the structure of a capacitor. When the gate-source voltage or gate-drain voltage exceeds a certain limit, it will cause the breakdown of the oxide film, causing The gate and the silicon under the oxide film are short-circuited. Once the oxide film is broken down, the MOS tube will be damaged, so when using the MOS tube, an excessively high voltage cannot be applied to the gate.

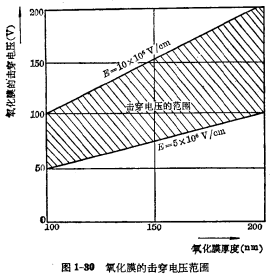

It is known from experiments that the breakdown voltage of the oxide film is proportional to the thickness of the oxide film, and the electric field strength E value of its breakdown is between 5×106~10×106V/cm. Under normal circumstances, the thickness of the oxide film under the gate is about 100~200nm, and its breakdown voltage is as shown in Figure 1-30. Because the quality of the oxide film 150nm is different, for the same thickness, the breakdown voltage The voltage is also different. The main parameters of MOS tube. For an oxide film with a thickness of 150nm, its breakdown voltage is between 75~120V. In fact, due to defects, pinholes and foreign contamination in SiO2, the maximum withstand voltage is reduced.

Since the gate capacitance of the MOS device is very small and the gate insulation resistance is very high, a very small amount of electricity will cause a very high voltage to make the gate breakdown. If the gate capacitance is 2pF, then only 1.5×10-10C of electricity can cause the gate and the substrate to reach The high voltage of 75V breaks down the gate oxide layer. After the gate breakdown, the gate current increases rapidly. Some people have found that the current density at the breakdown point can reach  spectrum The observed peak temperature is close to 4000K.

spectrum The observed peak temperature is close to 4000K.

(2)Gate protection

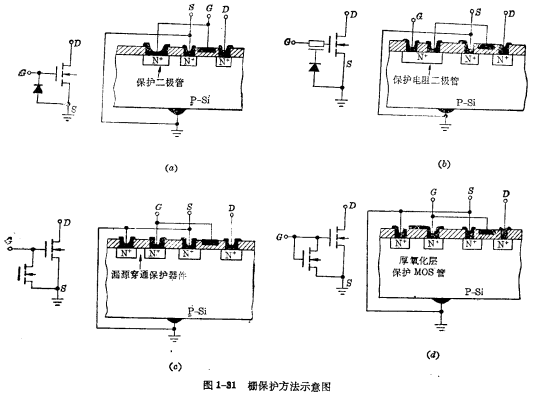

The prevention of barrier breakdown is a very important issue. There are many ways to prevent grid breakdown. For example, all instruments, power supplies, and soldering irons must be well grounded, and devices must be wrapped with conductive materials when they are not in use. However, none of these methods can make the gate completely protected. Therefore, people have come up with the use of gate to protect the device so that the gate of the device will not be easily broken down. For MOS circuits, in addition to paying attention to electrostatic breakdown during use and storage, protection devices must also be manufactured inside the circuit. There are many methods, but the basic principles are similar. Generally, there is a contact resistance and a parallel protection element between the outer lead and the grid. This component has a large resistance within the normal operating voltage range, so it does not affect the normal operation of the circuit, but when the gate voltage exceeds a certain range (for example, close to the gate breakdown voltage), its resistance becomes very small, and it is at the input A low-resistance path is formed at the end to discharge the induced static charge, so that the gate is protected. Figure 1-31 shows several commonly used input gate protection methods.

Among them, Figure 1-31 (a) is a diode protection. The reverse breakdown voltage of the diode is pre-designed to be lower than the gate breakdown voltage BVGS of the MOS tube. When the input voltage is greater than the reverse breakdown voltage of the diode for some reason, it provides a static discharge circuit to protect the gate of the MOS tube. Figure 1-31(b) is a series of diffused resistors in the input gate, and then a reverse diode in parallel. Figure 1-31(c) shows the drain-source punch-through protection device, whose punch-through breakdown voltage is lower than the gate breakdown voltage. Figure 1-31 (d) is a field inversion protection device, and its gate dielectric is a thick oxide layer, which is about ten times that of a MOS tube. The main parameters of MOS tube. As mentioned before, the threshold voltage of the MOS transistor is proportional to the thickness of the oxide layer. The thicker the oxide layer, the greater the VT. Therefore, when the gate has a high voltage input, the field inversion device is first turned on, providing a static discharge circuit, so that the gate of the MOS tube is protected.

Contact: Mr. Zou

Contact number:0755-83888366-8022

Mobile phone:18123972950

QQ:2880195519

Contact Address: 5C1, Block CD, Tianji Building, Tianan Digital City, Chegongmiao, Futian District, Shenzhen

Please search WeChat official account: "KIA Semiconductor" or scan the following picture to "Follow" official WeChat official account

Please "follow" the official WeChat account: provide MOS tube technical assistance