Electronic Technology Forum

Definition and Analysis of Threshold Voltage of MOS Device

Threshold voltage of MOS device

1、Threshold voltageVT

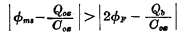

The so-called threshold voltage of a MOS device refers to the gate voltage when the drain source of the device is just turned on. This actually satisfies the strong inversion condition on the Si surface, that is, the surface potential . MOS threshold voltage. So how much gate voltage must be added to meet the strong inversion condition? If the source is grounded, the gate voltage here refers to the gate-source voltage VGS.

. MOS threshold voltage. So how much gate voltage must be added to meet the strong inversion condition? If the source is grounded, the gate voltage here refers to the gate-source voltage VGS.

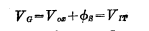

It is known from the previous analysis that for an actual MOS device to achieve strong inversion, the flat band condition must first be established. A voltage must be applied to the gate to offset the effect of the difference in work function and effective surface charge on the energy band and flatten the energy band. This flatband voltage is given by the sum of (1-18) and (1-20), namely:

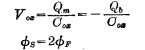

On the basis of the flat belt, a voltage must be applied to the grid to achieve the strong inversion condition. The voltage (1-1) formula gives:

here,

所以,

is called the intrinsic valve voltage, which is the threshold voltage of an ideal MOS device.

is called the intrinsic valve voltage, which is the threshold voltage of an ideal MOS device. Is the amount of charge per unit area in the space charge region.MOS threshold voltage. For N-type material,

Is the amount of charge per unit area in the space charge region.MOS threshold voltage. For N-type material, For P-type materials,

For P-type materials,  is a negative value.

is a negative value.

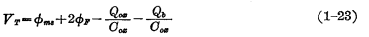

Add (1-21) and (1-22) together to get the expression of the threshold voltage of the MOS device:

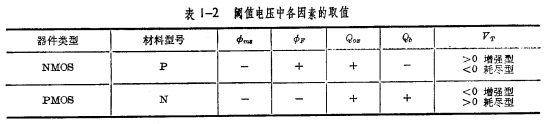

The formula (1-23) is obtained by analyzing the N-channel MOS system, but it is a general formula and also suitable for P-channel MOS devices. For different materials, the positive and negative values of each factor in the threshold voltage formula are different, which can be summarized in Table 1-2.

It can be seen from the table that for P-channel MOS devices with N-type substrates (1-23), the four symbols in the formula are the same ( is generally less than zero), which can be understood as adding the absolute value of the four items, and adding a minus sign before the sum. Therefore, the N-type substrate is always made of enhanced devices, and its threshold voltage VTIs negative. For N-channel MOS devices, due to the P-type substrate

is generally less than zero), which can be understood as adding the absolute value of the four items, and adding a minus sign before the sum. Therefore, the N-type substrate is always made of enhanced devices, and its threshold voltage VTIs negative. For N-channel MOS devices, due to the P-type substrate  , So the following situations may occur, namely:

, So the following situations may occur, namely:

In this case, the threshold voltage is negative, indicating that the channel has been formed and has become a depletion device. In the production of N-channel enhancement mode MOS transistors, the surface is often prone to surface depletion, so effective measures must be taken, for example, the resistivity of the substrate must be very low.(Generally at least below  ),In the process, try to reduce the effective positive charge density in the oxide layer, so that the inequality sign of the above inequality is reversed, namely:

),In the process, try to reduce the effective positive charge density in the oxide layer, so that the inequality sign of the above inequality is reversed, namely:

In this way, an N-channel enhancement type device with a positive VT can be obtained.

For enhanced devices, the threshold voltage always increases with the thickness of the oxide layer. For depletion devices, the same is true for the actual situation.

The following examples illustrate the typical data of each item in the threshold voltage. MOS threshold voltage. The threshold voltage of common P-channel MOS devices is -4V, and the doping concentration of the N-type substrate is about  The thickness of the oxide layer

The thickness of the oxide layer According to the above data, first check Figure 1-10 to get

According to the above data, first check Figure 1-10 to get Check Figure 1-18 again

Check Figure 1-18 again , And then calculate

, And then calculate

From this example, we can see that the reading voltage of a general P-channel MOS transistor is mainly determined by  Three decisions. It can be seen that the choice of substrate resistivity and the process

Three decisions. It can be seen that the choice of substrate resistivity and the process The control of is an important factor in determining the threshold voltage.

The control of is an important factor in determining the threshold voltage.

2. The impact of short channel effect on VT

When we derive the VT formula above, the channel of the MOS transistor considered is), and the influence of the drain and source diffusion region depletion layer on VT can no longer be ignored. Generally speaking, the VT of a short-channel MOS transistor is smaller than the VT of a channel MOS transistor. In the case of short channel,VTNot only with The substrate concentration N is related to

The substrate concentration N is related to  ,It is also related to the channel length L and the junction depth of the drain and source diffusion regions

,It is also related to the channel length L and the junction depth of the drain and source diffusion regions Related, Figure 1-15 shows the experimental relationship curve between MOS transistor VT and channel length L. It can be seen that the shorter the channel, the faster the rate of VT reduction. The reason for this effect is the charge density of ionized impurities in the channel depletion layer

Related, Figure 1-15 shows the experimental relationship curve between MOS transistor VT and channel length L. It can be seen that the shorter the channel, the faster the rate of VT reduction. The reason for this effect is the charge density of ionized impurities in the channel depletion layer The contribution to VT is reduced. MOS threshold voltage. In the case of long channels,It can be considered that all the

The contribution to VT is reduced. MOS threshold voltage. In the case of long channels,It can be considered that all the  below the channel L are all right to VT contributed,In the case of a short channel, since the source and drain diffusion regions at both ends of the channel have an increased influence on the electrostatic potential distribution in the channel, a part of the power lines of the depletion layer ionizing impurity charges in the source and drain diffusion regions will end in the channel. The following depletion zone is shown in Figure 1-16.In this way, it weakens the

below the channel L are all right to VT contributed,In the case of a short channel, since the source and drain diffusion regions at both ends of the channel have an increased influence on the electrostatic potential distribution in the channel, a part of the power lines of the depletion layer ionizing impurity charges in the source and drain diffusion regions will end in the channel. The following depletion zone is shown in Figure 1-16.In this way, it weakens the  to VT’s contribution. It can also be considered that the ionized impurities in the depletion region under the channel

to VT’s contribution. It can also be considered that the ionized impurities in the depletion region under the channel It is reduced, so VT is reduced.

It is reduced, so VT is reduced.

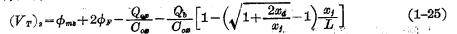

According to theoretical calculation, the threshold voltage Vr of the short-channel MOS transistor is:

In Is the diffusion depth of the source and drain diffusion regions, L is the channel length,

Is the diffusion depth of the source and drain diffusion regions, L is the channel length,  is the width of the depletion zone. It can be seen from the formula (1-25) that in order to reduce the influence of the channel length of the short-channel MOS transistor on VT, the drain and source must be reduced. The junction depth of the diffusion zone

is the width of the depletion zone. It can be seen from the formula (1-25) that in order to reduce the influence of the channel length of the short-channel MOS transistor on VT, the drain and source must be reduced. The junction depth of the diffusion zone

,Or increase the substrate impurity concentration N.

,Or increase the substrate impurity concentration N.

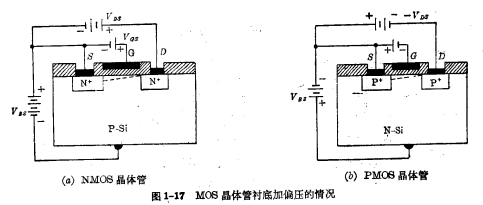

3、The number of grids on the back side responds to the influence of VT

When a MOS transistor is used as a single tube, its source and substrate are connected together and grounded together. But when MOS transistors form a circuit, the source of some tubes is not directly connected to the bottom of the village, for example,

A certain bias voltage Vas is applied between the substrate and the source. As shown in Figure 1-17.

When a bias voltage is applied between the source electrode and the substrate, the PN junction between the source diffusion region and the substrate is in a reverse bias. In this way, the channel is modulated by the substrate bias voltage. This effect is commonly referred to as the "back-side gate" effect, or "substrate bias effect."

As seen from Figure 1-17, the reverse bias voltage  It is added between the channel and the substrate through the source. Because the channel is very thin, it can be seen as the N+ region of the unilateral mutation PN junction. The result of the reverse bias will be The depletion layer between the channel and the substrate is widened to the inside of the substrate, and the charge in the depletion layer increases. Since the electric medium condition of the MOS system is to be maintained, the electron charge in the channel must be reduced and the channel becomes thinner. MOS threshold voltage. If the original channel width is to be maintained, more positive charges must be accumulated on the gate to balance the increased negative charges in the depletion layer. This means increasing the threshold voltage

It is added between the channel and the substrate through the source. Because the channel is very thin, it can be seen as the N+ region of the unilateral mutation PN junction. The result of the reverse bias will be The depletion layer between the channel and the substrate is widened to the inside of the substrate, and the charge in the depletion layer increases. Since the electric medium condition of the MOS system is to be maintained, the electron charge in the channel must be reduced and the channel becomes thinner. MOS threshold voltage. If the original channel width is to be maintained, more positive charges must be accumulated on the gate to balance the increased negative charges in the depletion layer. This means increasing the threshold voltage

The channel becomes thinner or even disappears. This means that the greater the absolute value of the bias voltage

The channel becomes thinner or even disappears. This means that the greater the absolute value of the bias voltage  , the greater the absolute value of the valve Increase in value voltage

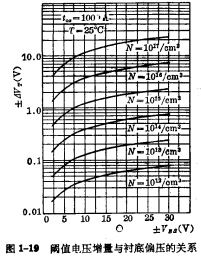

, the greater the absolute value of the valve Increase in value voltage Also bigger. Figure 1-18 shows how the channel changes with

Also bigger. Figure 1-18 shows how the channel changes with  . Where (a) is

. Where (a) is  The channel is not modulated; (b) is

The channel is not modulated; (b) is

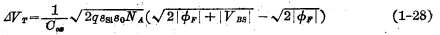

The magnitude of can be obtained from the expression of the threshold voltage. After the source and substrate are applied with a reverse bias voltage, the energy band is more bent, and the charge density in the space charge region increases, and the amount is given by the following formula:

The magnitude of can be obtained from the expression of the threshold voltage. After the source and substrate are applied with a reverse bias voltage, the energy band is more bent, and the charge density in the space charge region increases, and the amount is given by the following formula:

So the expression of the threshold voltage can be changed to:

Subtract (1-27) from (1-23) to get:

If it is a P-channel MOS tube, when there is a bias voltage image.png between the substrate and the source, as shown in Figure 1-17 (b), the threshold voltage increment is:

According to the above analysis:

For N-channel MOS transistors, because

So get

So get  For P channel from (1-28), (1 -29) The two formulas show that

For P channel from (1-28), (1 -29) The two formulas show that It is closely related to the substrate concentration and the magnitude of the bias voltage. As shown in Figure 1-19. Road MOS transistor, because

It is closely related to the substrate concentration and the magnitude of the bias voltage. As shown in Figure 1-19. Road MOS transistor, because

In engineering calculations, for the sake of convenience, the increment of the threshold voltage often adopts an approximate expression:

In the formula is the substrate bias effect constant, which varies with the substrate doping concentration, and its typical value is: For N-channel MOS transistors, For P-channel MOS transistors,

For P-channel MOS transistors,

Finally, we have to emphasize one point about VT. The threshold voltage of the MOS device mentioned above is the threshold voltage VT,It is exactly the gate voltage when the channel is formed, and has nothing to do with the geometry of the tube. MOS threshold voltage. But in actual production, VTIt is often set as the drain-source current as

Finally, we have to emphasize one point about VT. The threshold voltage of the MOS device mentioned above is the threshold voltage VT,It is exactly the gate voltage when the channel is formed, and has nothing to do with the geometry of the tube. MOS threshold voltage. But in actual production, VTIt is often set as the drain-source current as The gate voltage applied at the time is not exactly the same as the one mentioned above. Because the threshold voltage set at

The gate voltage applied at the time is not exactly the same as the one mentioned above. Because the threshold voltage set at  is often still to a certain extent Depends on the geometric size, so the valve voltage measured in the production is larger than the valve voltage mentioned above.

is often still to a certain extent Depends on the geometric size, so the valve voltage measured in the production is larger than the valve voltage mentioned above.

Contact: Mr. Zou

Contact number:0755-83888366-8022

Mobile phone:18123972950

QQ:2880195519

Contact Address: 5C1, Block CD, Tianji Building, Tianan Digital City, Chegongmiao, Futian District, Shenzhen

Please search WeChat official account: "KIA Semiconductor" or scan the following picture to "Follow" official WeChat official account

Please "follow" the official WeChat account: provide MOS tube technical assistance